## **BUKU DARAS**

# ORGANISASI & ARSITEKTUR KOMPUTER

Disusun oleh:

Faisal, S.T, M.T

JURUSAN TEKNIK INFORMATIKA UIN ALAUDDIN MAKASSAR 2015

#### KATA PENGANTAR

Puji syukur penulis panjatkan kehadirat Allah swt, atas segala rahmat dan hidayahNya sehingga penulis mampu menyelesaikan buku yang sederhana ini dengan segala kekurangannya. Buku ini disusun dalam rangka mengimplementasikan integrasi keilmuan antara disiplin ilmu komputasi yang dikaitkan dengan kajian-kajian ayat Al-Qur'an yang berhubungan dengannya, sehingga kita sebagai manusia semakin menyadari bahwa ilmu yang kita miliki hanyalah setetes air ditengah lautan ilmu yang dimiliki Allah swt.

Buku ini merupakan bahan kuliah Organisasi dan Arsitektur Komputer selama satu semester dengan bobot teori 2 SKS ditambah dengan praktikum 1 SKS, dan merupakan mata kuliah wajib di jurusan Teknik Informatika UIN Alauddin Makassar. Buku ini berisi 11 satuan bahasan yang masing-masing membahas tentang: Pengantar Organisasi dan Aristektur Komputer; Evolusi dan Kinerja Komputer; Sistem Bilangan; Gerbang Logika Dasar dan Aljabar Boole; Rangkaian Logika Kombinasi; Rangkaian Logika Sekuensial; Central Processing Unit (CPU); Memori Utama; Memori Sekunder; Peralatan Input/Output; dan Sistem Bus.

Dengan membaca buku ini, diharapkan mahasiswa dan para pembaca dapat memahami konsep-konsep dari organisasi dan arsitektur komputer itu sendiri, dan dalam prakteknya mahasiswa mampu mengenali berbagai jenis komponen dan fungsinya sebagai pembentuk dari perangkat komputer. Betapa besar kekuasaan Allah swt telah menciptakan manusia sebagai makhluk yang paling mulia dan dengan ilmu yang dimilikinya telah menciptakan perangkat komputer yang sangat membantu aktifitas manusia sehari-hari.

Pada kesempatan ini penulis ingin menyampaikan ucapan terima kasih yang sebesar-besarnya kepada semua pihak baik langsung maupun tidak langsung, yang telah banyak memberikan bantuan, saran dan kritikan, sehingga penulisan buku ini dapat terwujud. Ucapan terima kasih penulis sampaikan kepada Rektor UIN Alauddin Makassar, Kepala LP2M, Dekan Fakultas Sains & Teknologi, rekanrekan dosen, dan segenap pihak yang tidak sempat disebutkan satu per satu, serta terkhusus kepada keluarga tercinta atas segala dukungan dan bantuannya mulai dari tahap awal hingga rampungnya buku ini. Semoga Allah swt menerima kebaikan semuanya dan menjadikan sebagai catatan amaliah disisiNya.

Pada akhirnya penulis menyadari akan keterbatasan ilmu dan pengetahuan yang dimiliki sehingga apa yang tersaji dalam buku ini masih jauh dari kesempurnanaan. Tak ada gading yang tak retak. Oleh karena itu, segala kritik, saran dan masukan yang membangun, sangat penulis harapkan demi perbaikan buku ini untuk penerbitan selanjutnya.

Semoga buku ini ada manfaatnya untuk kepentingan akademik, bangsa dan agama, serta mampu menjadi pelita dunia ilmiah di tanah air. Aamiiinn ya Rabbal aalamiiin.

Makassar, Agustus 2015

**PENULIS**

# DAFTAR ISI

| Sambutan Rektor UIN Alauddin Makassar                 | iii |

|-------------------------------------------------------|-----|

| Kata Pengantar                                        | iv  |

| Daftar Isi                                            | vi  |

| Daftar Gambar                                         | X   |

| Daftar Tabel                                          | xii |

|                                                       |     |

|                                                       |     |

| Satuan Bahasan 1:                                     |     |

| Pengantar Organisasi dan Arsitektur Komputer          | 1   |

| 1.1. Komputer                                         | 2   |

| 1.2. Pengertian Organisasi dan Arsitektur Komputer    | 4   |

| 1.3. Struktur dan Fungsi Utama Komputer               | 4   |

| 1.3.1. Struktur Komputer                              | 4   |

| 1.3.2. Fungsi Komputer                                | 5   |

| Rangkuman                                             | 7   |

| Tes Formatif                                          | 8   |

|                                                       |     |

|                                                       |     |

| Satuan Bahasan 2:                                     |     |

| Evolusi dan Kinerja Komputer                          | 9   |

| 2.1. Sejarah Perkembangan Komputer                    | 10  |

| 2.1.1. Komputer Primitif                              | 10  |

| 2.1.2. Generasi Pertama: Tabung Vakum (1945-1955)     | 11  |

| 2.1.3. Generasi Kedua: Transistor(1955-1965)          | 15  |

| 2.1.4. Generasi Ketiga: Integrated Circuit(1965-1980) | 17  |

| 2.1.5. Generasi Keempat: Very Large Scale Integrated  | 1 / |

| (1980-sekarang)                                       | 18  |

| 2.2. Perancangan Kinerja                              | 19  |

| 2.3. Contoh Evolusi Komputer                          | 21  |

| Rangkuman                                             | 23  |

| Tes Formatif                                          | 24  |

| 1Co I Officati                                        | 47  |

|                                                       |     |

| Satuan Bahasan 3:                                     |     |

| Sistem Bilangan                                       | 25  |

| 3.1. Jenis Sistem Bilangan                            | 26  |

| 3.2. Sistem Bilangan Desimal                          | 26  |

| 3.3. Sistem Bilangan Binari (Biner)                   | 28  |

| 3.4. Sistem Bilangan Oktal                            | 28  |

| 3.5. Sistem Bilangan Hexadesimal                      | 29  |

| 3.6. Konversi Sistem Bilangan                         | 30  |

| 3.6.1. Konversi Sistem Bilangan Desimal               | 30  |

| 3.6.2. Konversi Sistem Bilangan Binari                | 32  |

| J.O.Z. IXOHYCEOLOGOGHI DHangall DHall                 | 52  |

| 3.6.3. Konversi Sistem Bilangan Oktal                    |

|----------------------------------------------------------|

| 3.6.4. Konversi Sistem Bilangan Hexadesimal              |

| 3.7. Sistem Kode                                         |

| 3.7.1. Kode BCD (Binary-Coded Decimal)                   |

| 3.7.2. Kode Excess-3                                     |

| 3.7.3. Kode Gray                                         |

| 3.7.4. Kode 7-Segment Display                            |

| 3.7.5. Kode ASCII                                        |

| Rangkuman                                                |

| Tes Formatif                                             |

|                                                          |

|                                                          |

| Satuan Bahasan 4:                                        |

| Gerbang Logika Dasar & Aljabar Boole                     |

| 4.1. Tabel Kebenaran                                     |

| 4.2. Gerbang Logika Dasar                                |

| 4.2.1. AND Gate                                          |

| 4.2.2. OR Gate                                           |

| 4.2.3. NOT Gate                                          |

| 4.2.4. NAND Gate                                         |

| 4.2.5. NOR Gate                                          |

| 4.2.6. EX-OR Gate                                        |

| 4.2.7. EX-NOR Gate                                       |

| 4.3. Teorema-teorema Aljabar Boole                       |

| 4.3.1. Teorema Variabel Tunggal                          |

| 4.3.2. Teorema Variabel Jamak                            |

| Rangkuman                                                |

| Tes Formatif 51                                          |

| Tes romiaul                                              |

|                                                          |

| Satuan Bahasan 5:                                        |

|                                                          |

| Rangkaian Logika Kombinasi                               |

| $\mathcal{O}$                                            |

| O                                                        |

| 5.2.1. Bentuk <i>Sum Of Product (SOP)</i>                |

| 5.2.2. Bentuk <i>Product Of Sum (POS)</i>                |

| 5.2.3. Mengubah Fungsi Bentuk Tak Standar Menjadi Bentuk |

| Standar                                                  |

| 5.3. Penyederhanaan Secara Aljabar                       |

| Rangkuman                                                |

| Tes Formatif                                             |

|                                                          |

|                                                          |

| Satuan Bahasan 6:                                        |

| Rangkaian Logika Sekuensial                              |

| 6.1. Flip Flop                     | 75         |

|------------------------------------|------------|

|                                    | 75         |

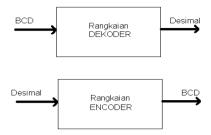

| 6.2. Encoder dan Decoder           | 35         |

| 6.3. Multiplexer dan Demultiplexer | 94         |

|                                    | 98         |

|                                    | 99         |

|                                    |            |

|                                    |            |

| Satuan Bahasan 7:                  |            |

| Central Processing Unit            | 00         |

| 7.1. Komponen Utama CPU            | )1         |

| 7.2. Fungsi CPU                    | )3         |

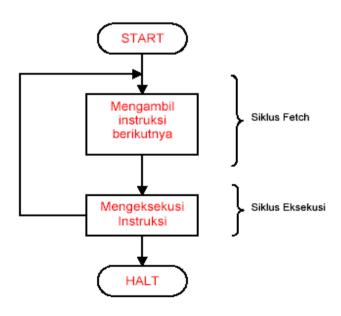

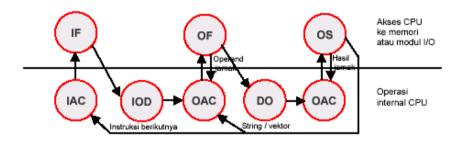

| 7.2.1. Siklus Fetch-Eksekusi       | )3         |

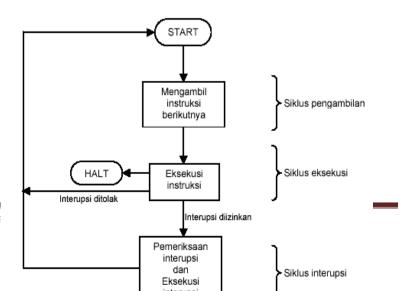

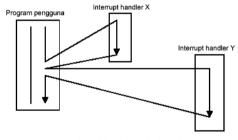

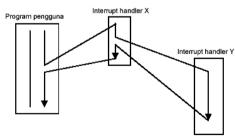

| 7.2.2. Fungsi Interrupt            | )5         |

| Rangkuman                          | )8         |

| Tes Formatif10                     | )8         |

|                                    |            |

|                                    |            |

| Satuan Bahasan 8:                  |            |

| Memori Utama                       |            |

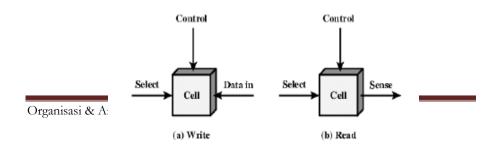

| 8.1. Operasi Sel Memori            |            |

| 8.2. Karakteristik Sistem Memori   |            |

| 8.3. Keandalan Memori              |            |

| 8.4. Satuan Memori                 | 15         |

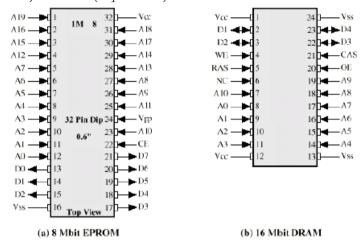

| 8.5. Memori Utama Semikonduktor    | 15         |

| 8.5.1. Jenis Memori Random Akses   | 15         |

| 8.5.2. Pengemasan (Packaging)      | 17         |

| 8.5.3. Koreksi Error               | 18         |

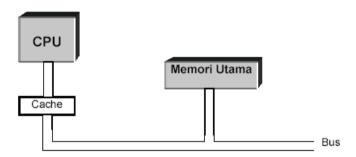

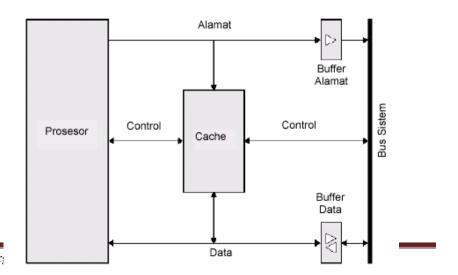

| 8.6. Cache Memori                  | 22         |

| 8.7. Elemen Rancangan              | 24         |

| 8.7.1. Kapasitas Cache             | 24         |

| 8.7.2. Ukuran Blok                 | 25         |

| 8.7.3. Fungsi Pemetaan (Mapping)   | 25         |

| 8.7.4. Algoritma Penggantian       | 27         |

| 8.7.5. Write Policy                | 28         |

| 8.7.6. Jumlah Cache                | 29         |

| Rangkuman                          |            |

| Tes Formatif                       | 30         |

|                                    |            |

|                                    |            |

|                                    |            |

|                                    |            |

| Satuan Bahasan 9:                  |            |

| Memori Sekunder                    |            |

| 13                                 | <i>i</i> 1 |

|                                           | 31  |

|-------------------------------------------|-----|

|                                           | 38  |

| 1                                         | 41  |

| O                                         | 46  |

|                                           | 47  |

| Tes formatif                              | 48  |

|                                           |     |

| Satuan Bahasan 10:                        |     |

| Paralatan Input/Output                    |     |

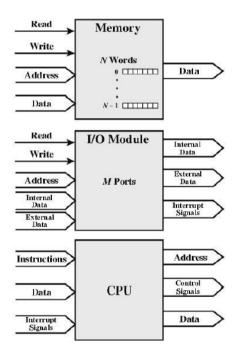

| 10.1 Sistem Masukan dan Keluaran Komputer | 49  |

| 10.1.1. Fungsi Modul I/O                  | 50  |

|                                           | 51  |

| 10.1.2. Struktur Modul I/O                | 53  |

| 10.2. Teknik Masukan/Keluaran             | 54  |

| 10.2.1. I/O Terprogram                    | 54  |

| 10.2.2. Interrpt-Driven I/O               | 56  |

| 10.2.3. Direct Memory Access (DMA)        | 60  |

| 10.3. Perangkat Eksternal                 | 62  |

| Rangkuman                                 | 63  |

| Les Hormatit                              | 63  |

| -                                         | -   |

| Satuan Bahasan 11:                        |     |

| Sistem BUS                                |     |

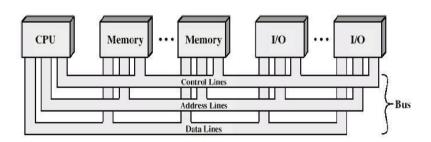

| 11.1 Struktur Interkoneksi                | 64  |

| 11.2. Interkoneksi Bus                    | 65  |

| 11.3. Elemen Perancangan Bus              | 67  |

| 11.4. Contoh Bus                          | 70  |

| 11.4.1. Bus ISA                           | 73  |

|                                           | 73  |

| 11.4.2. Bus PCI                           | 74  |

| 11.4.3. Bus USB                           | 74  |

| 11.4.4. Bus SCSI                          | 75  |

| 11.4.5. Dus P1394/ Firewire               | 76  |

| Kangkuman                                 | 76  |

| Les Hormatit                              | 77  |

|                                           | . , |

| Daftar Pustaka                            | 78  |

| 1,                                        |     |

# **DAFTAR GAMBAR**

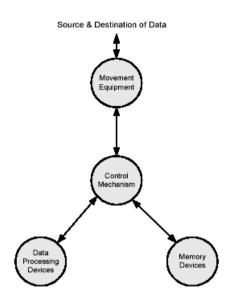

| Gambar 1.1. Unit Fungsional Dasar pada Komputer          | 3  |

|----------------------------------------------------------|----|

| Gambar 1.2. Struktur Dasar Komputer                      | 5  |

| Gambar 1.3. Fungsi Dasar Komputer                        | 6  |

| Gambar 1.4. Operasi-operasi Komputer                     | 7  |

| Gambar 2.1. John von Neumann                             | 12 |

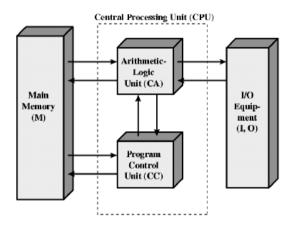

| Gambar 2.2. Struktur Komputer IAS                        | 13 |

| Gambar 2.3. Format Memori IAS                            | 13 |

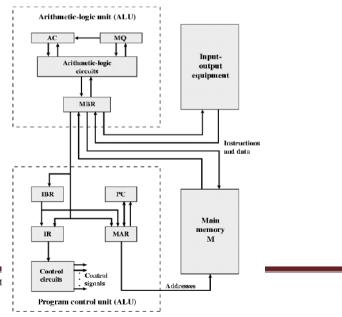

| Gambar 2.4. Struktur Detail Komputer IAS                 | 14 |

| Gambar 2.5. Konfigurasi IBM 7094                         | 16 |

| Gambar 2.6. Struktur Bus PDP-8                           | 18 |

| Gambar 2.7. Grafik Jumlah Transistor dalam Chip Pentium  | 19 |

| Gambar 2.8. Grafik Perbandingan Kecepatan Mikroprosesor  |    |

| dan Memori                                               | 20 |

| Gambar 3.1. Bobot Nibble                                 | 29 |

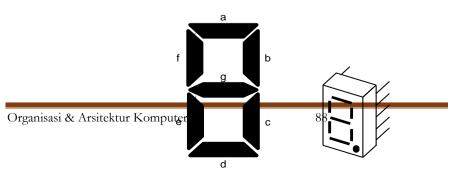

| Gambar 3.2. Peraga 7-Segmen                              | 39 |

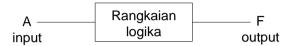

| Gambar 4.1. Diagram Blok Rangkaian Logika Satu Variabel  |    |

| Input                                                    | 43 |

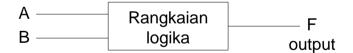

| Gambar 4.2. Diagram Blok Rangkaian Logika Dua Variabel   |    |

| Input                                                    | 43 |

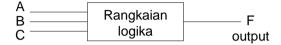

| Gambar 4.3. Diagram Blok Rangkaian Logika Tiga Variabel  |    |

| Input                                                    | 44 |

| Gambar 4.4. Simbol Gerbang AND                           | 45 |

| Gambar 4.5. Simbol Gerbang OR                            | 46 |

| Gambar 4.6. Simbol Gerbang NOT                           | 46 |

| Gambar 4.7. Simbol Gerbang NAND                          | 47 |

| Gambar 4.8. Simbol Gerbang NOR                           | 47 |

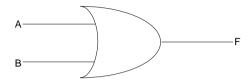

| Gambar 4.9. Simbol Gerbang EX-OR                         | 48 |

| Gambar 4.10. Simbol Gerbang EX-NOR                       | 48 |

| Gambar 5.1. Diagram Blok Rangkaian Logika Kombinasi      | 53 |

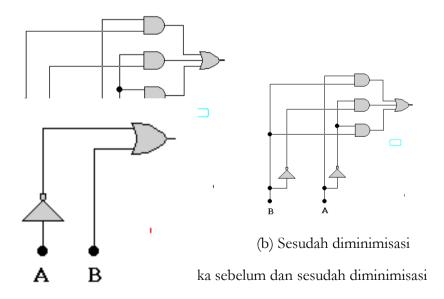

| Gambar 5.2. Rangkaian Logika Sebelum dan Sesudah         |    |

| Diminimisasi                                             | 61 |

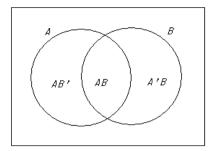

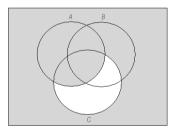

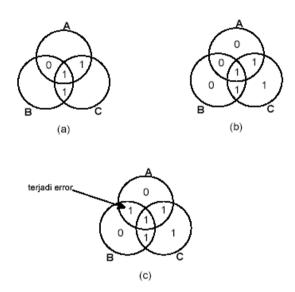

| Gambar 5.3. Diagram Venn                                 | 64 |

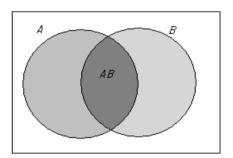

| Gambar 5.4. Diagram Venn untuk irisan dua variabel       | 64 |

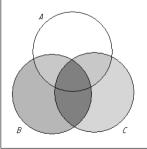

| Gambar 5.5. Diagram Venn untuk irisan tiga variabel      | 64 |

| Gambar 5.6. Karnaugh Map untuk 2 variabel input          | 65 |

| Gambar 5.7. Karnaugh Map untuk 3 variabel input          | 65 |

| Gambar 5.8. Karnaugh Map untuk 4 variabel input          | 66 |

| Gambar 5.9. Karnaugh Map untuk 6 variabel input          | 66 |

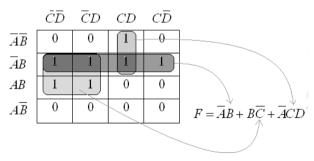

| Gambar 5.10. Contoh input data dari truth table ke K-Map | 66 |

| Gambar 5.11. Input Nilai Logic 1 dalam K-Map             | 67 |

| Gambar 5.12. K-Mapmembentuk persamaan logika sederhana   | 67 |

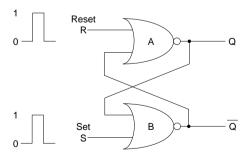

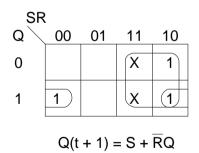

| Gambar 6.1. Rangkaian Flip Flop Dasar dengan Gerbang<br>NOR |  |

|-------------------------------------------------------------|--|

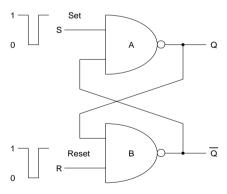

| Gambar 6.2. Rangkaian Flip Flop Dasar dengan Gerbang NAND   |  |

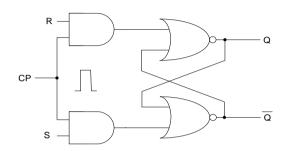

| Gambar 6.3. Daigram Logika Flip Flop RS                     |  |

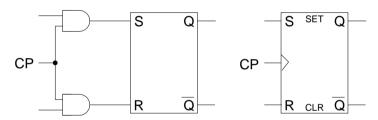

| Gambar 6.4. Lambang Tanpa dan Dengan Pulsa Waktu            |  |

|                                                             |  |

| Gambar 6.5. Persamaan Karakteristik                         |  |

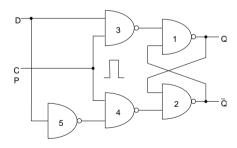

| Gambar 6.6. Diagram Logika Flip Flop D                      |  |

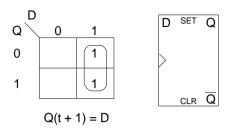

| Gambar 6.7. Lambang dan Persamaan Karakteristik             |  |

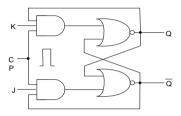

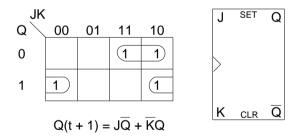

| Gambar 6.8. Diagram Logika Flip Flop JK                     |  |

| Gambar 6.9. Lambang dan Persamaan Karakteristik             |  |

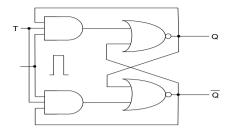

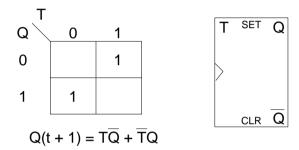

| Gambar 6.10 Diagram Logika Flip Flop T                      |  |

| Gambar 6.11. Lambang dan Persamaan Karakteristik            |  |

| Gambar 6.12. Encoder dan Decoder                            |  |

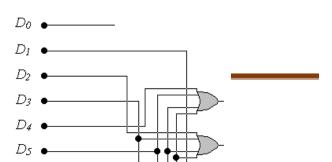

| Gambar 6.13. Rangkaian Encoder Oktal ke Biner               |  |

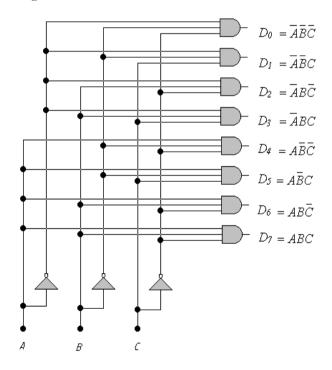

| Gambar 6.14. Rangkaian Decoder Biner ke Oktal               |  |

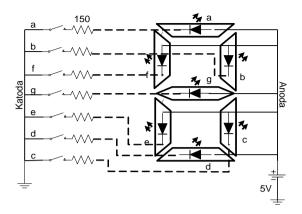

| Gambar 6.15. Seven Segment                                  |  |

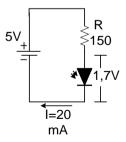

| Gambar 6.16. Sirkit untuk menyalakan LED                    |  |

| Gambar 6.17. Azas Menyalakan LED                            |  |

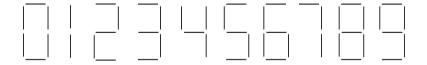

| Gambar 6.18. Angka-angka yang dapat ditampilkan oleh        |  |

| 7-Segment                                                   |  |

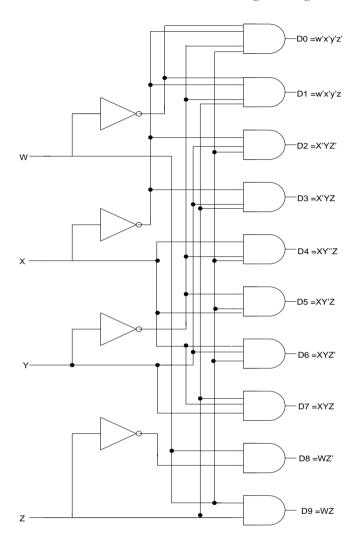

| Gambar 6.19. Decoder BCD ke Desimal                         |  |

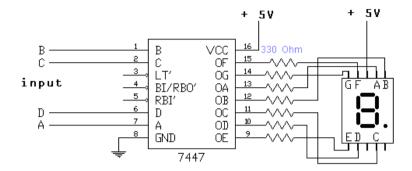

| Gambar 6.20. Rangkaian Decoder BCD to 7-Segmen common       |  |

| anoda                                                       |  |

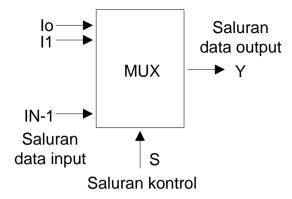

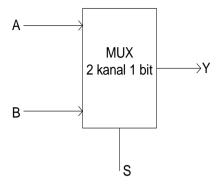

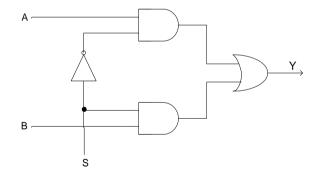

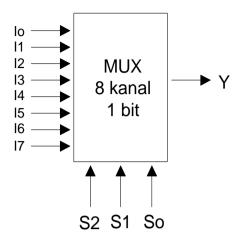

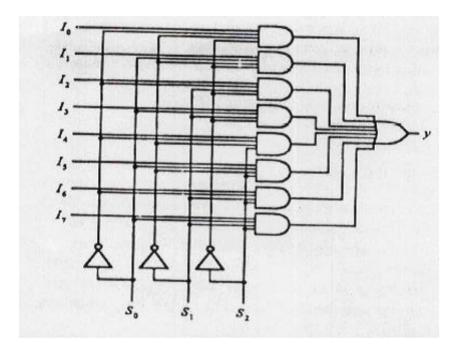

| Gambar 6.21. Diagram Multiplexer                            |  |

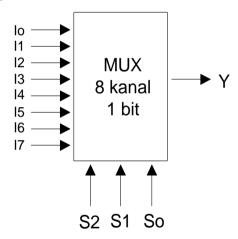

| Gambar 6.22. Diagram Multiplexer 8 kanal 1 bit              |  |

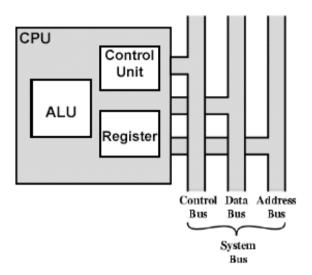

| Gambar 7.1. Komponen Internal CPU                           |  |

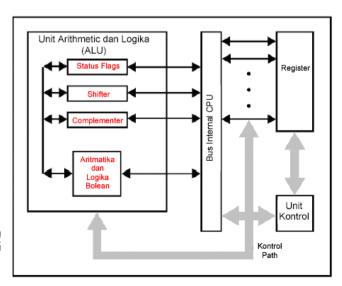

| Gambar 7.2. Struktur Detail Internal CPU                    |  |

| Gambar 7.3. Siklus Instruksi Dasar                          |  |

| Gambar 7.4. Diagram Siklus Insstruksi                       |  |

| Gambar 7.5. Siklus eksekusi Instruksi dengan Interupsi      |  |

| Gambar 7.6. Transfer Pengendalian pada interupsi Ganda      |  |

| Gambar 8.1. Operasi Sel Memori                              |  |

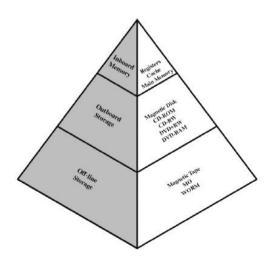

| Gambar 8.2. Hirarki Memori                                  |  |

| Gambar 8.3. Pin dan Sinyal Kemasan Memori                   |  |

| Gambar 8.4. Packaging SIMM                                  |  |

| Gambar 8.5. Koreksi Kesalahan dengan Kode Hamming           |  |

| Gambar 8.6. Hubungan Cache Memori                           |  |

| Gambar 8.7. Organisasi Cache Memori                         |  |

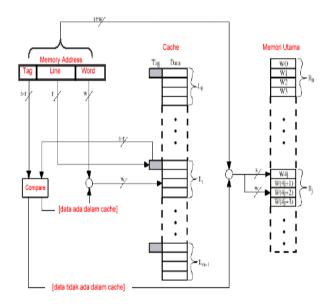

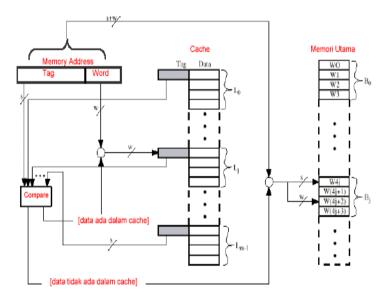

| Gambar 8.8. Organisasi Cache Pemetaan Langsung              |  |

| Gambar 8.9. Organisasi Cache Pemetaan Asosiatif             |  |

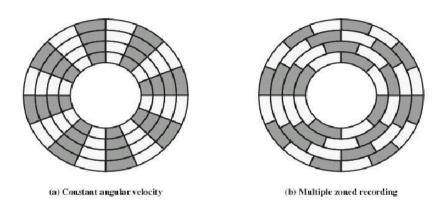

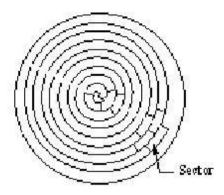

| Gambar 9.1. Layout Data Disk                                |  |

| Gambar 9.2. Metode Layout Data Disk                         |  |

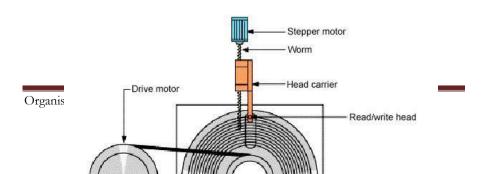

| Gambar 9.3. Macam Disk Berdasarkan Gerakan Head             |  |

| Gambar 9.4. Disk Piringan Banyak (Multipple Platter Disk)    | 3 |

|--------------------------------------------------------------|---|

| Gambar 9.5. Floppy Disk                                      | 1 |

| Gambar 9.6. Layout Disk CLV                                  | 7 |

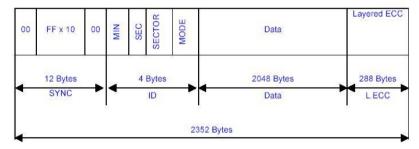

| Gambar 9.7. Format Blok CD-ROM                               | l |

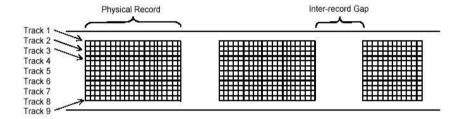

| Gambar 9.8. Format Fisik Pita Magnetik                       | 3 |

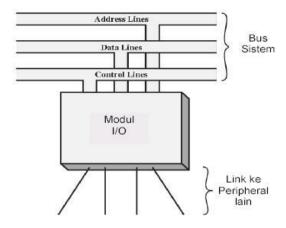

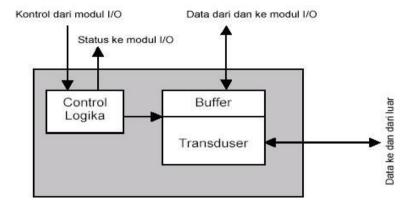

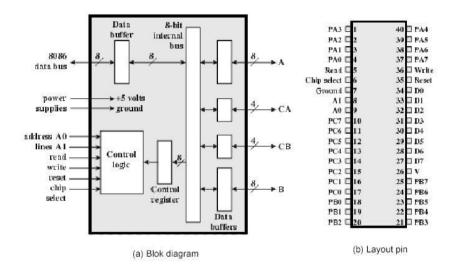

| Gambar 10.1. Model Generik dari suatu Modul I/O 154          | 1 |

| Gambar 10.2. Skema Suatu Perangkat Peripheral                |   |

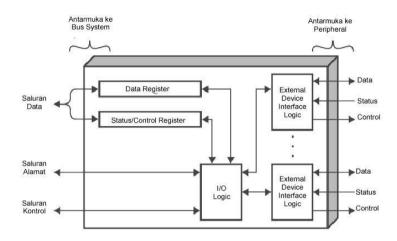

| Gambar 10.3. Blok Diagram Struktur Modul I/O 158             | 3 |

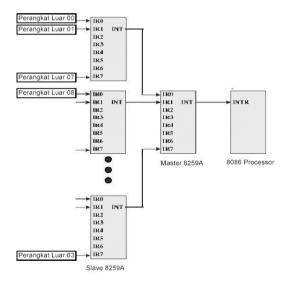

| Gambar 10.4. Pemakaian Pengontrol Interupsi 8559A pada 159   | ) |

| 8086                                                         |   |

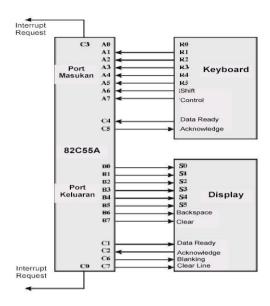

| Gambar 10.5. Modul I/O 8255A                                 | ) |

| Gambar 10.6. Interface Keyboard dan Display dengan Intel 161 | l |

| 8255A 161                                                    | l |

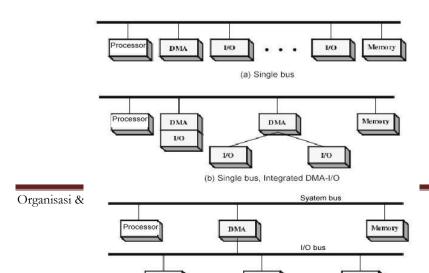

| Gambar 10.7. Blok Diagram DMA                                | 5 |

| Gambar 10.8. Konfigurasi Modul DMA                           | 7 |

| Gambar 11.1. Modul-modul Komputer                            | ) |

| Gambar 11.2. Pola Interkoneksi Bus                           | ) |

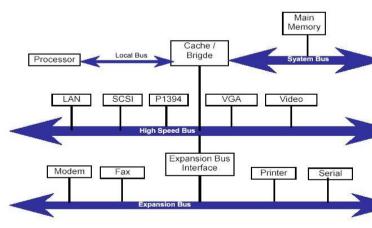

| Gambar 11.3. Arsitektur Bus Jamak Tradisional                | 2 |

| Gambar 11.4. Arsitektur Bus Jamak Berkinerja Tinggi          | 2 |

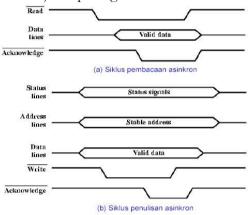

| Gambar 11.5. Contoh Pewaktuan Sinkron                        |   |

| Gambar 11.6. Contoh Pewaktuan Asinkron                       |   |

|                                                              |   |

# DAFTAR TABEL

| Tabel 2.1. Karakteristik Penting Kelompok Sistem/360            | 17    |

|-----------------------------------------------------------------|-------|

| Tabel 3.1. Posisi Value                                         | 27    |

| Tabel 3.2. Posisi Bilangan Binari                               | 28    |

| Tabel 3.3. Tabel Posisi Bilangan Oktal                          |       |

| Tabel 3.4. Posisi Bilangan Hexadesimal                          |       |

| Tabel 3.5. Digit Oktal                                          | 32    |

| Tabel 3.6. Digit Hexadesimal                                    | 33    |

| Tabel 4.1. Tabel Kebenaran Rangkaian Logika Satu Variabel Input |       |

| Tabel 4.2. Tabel Kebenaran Rangkaian Logika Dua Variabel        | • 43  |

| Input                                                           |       |

| Tabel 4.3. Tabel Kebenaran Rangkaian Logika Tiga Variabel       | 43    |

| Input                                                           |       |

| Tabel 4.4. Tabel Kebenaran Gerbang AND 2 Input                  | 44    |

| Tabel 4.5. Tabel Kebenaran Gerbang OR 2 Input                   | ·· 45 |

| Tabel 4.6. Tabel Kebenaran Gerbang NOT 2 Input                  | 46    |

| Tabel 4.7. Teorema-teorema Aljabar Boole untuk Variabel         | 47    |

| Tunggal                                                         |       |

| Tabel 4.8. Teorema-teorema Aljabar Boole untuk Variabel         | 49    |

| Jamak                                                           |       |

| Tabel 5.1. Tabel Kebenaran Fungsi X                             | 49    |

| Tabel 5.2. Tabel Kebenaran Fungsi R                             | . 56  |

| Tabel 5.3. Kelompok Jumlah Logika 1                             | 59    |

| Tabel 6.1. Tabel Kebenaran Flip Flop Dasar dengan Gerbang       | 3 68  |

| NOR                                                             |       |

| Tabel 6.2. Tabel Kebenaran Flip Flop Dasar dengan Gerbang       | 3 76  |

| NAND                                                            |       |

| Tabel 6.3. Tabel Karakteristik Flip Flop RS Menurut Waktu       |       |

| Tabel 6.4. Tabel Karakteristik Flip Flop D                      |       |

| Tabel 6.5. Tabel Karakteristik Flip Flop JK                     |       |

| Tabel 6.6. Tabel Karakteristik Flip Flop T                      |       |

| Tabel 6.7. Tabel Kebenaran Encoder Oktal ke Biner               |       |

| Tabel 6.8. Tabel Kebenaran Decoder Biner ke Oktal               |       |

| Tabel 6.9. Tabel Kebenaran Decoder BCD ke Desimal               |       |

| Tabel 6.10. Tabel Kebenaran Decoder common anoda                |       |

| Tabel 6.11. Tabel Kebenaran Decoder common katoda               |       |

| Tabel 8.1. Karakteristik Penting Sistem Memori Komputer         |       |

| Tabel 8.2. Tabel Spesifikasi Memori                             | 111   |

| Tabel 8.3. Tingkatan Satuan Memori                              | 115   |

| Tabel 8.4. Tipe-tipe Memori Semikonduktor                       | 115   |

| Tabel 8.5. Penambahan Bit Cek Paritas untuk koreksi kode        | 117   |

| Hamming                                                         | 120   |

| Tabel 8.6. Unsur-unsur Rancangan Cache Memori  | 124 |

|------------------------------------------------|-----|

| Tabel 9.1. Karakteristik Magnetik Disk         | 133 |

| Tabel 9.2. Karakteristik Berbagai Macam Disket | 137 |

| Tabel 9.3. Versi Disk SCSI                     | 138 |

#### **SATUAN BAHASAN 1**

# PENGANTAR ORGANISASI DAN ARSITEKTUR KOMPUTER

#### 1. Gambaran Singkat Mengenai Materi Kuliah

Materi kuliah dari satuan bahasan yang pertama ini berisikan tentang pengertian dari komputer, perbedaan antara organisasi dengan arsitektur komputer. Juga membahas tentang fungsi dan struktur dasar dari komputer.

### 2. Pedoman Mempelajari Materi

Baca dengan cermat dan teliti materi pada satuan bahasan 1, kemudian pahami setiap teori yang akan membantu pemahaman anda tentang organisasi dan arsitektur komputer itu sendiri. Pada akhir satuan bahasan terdapat tes formatif yang perlu anda kerjakan sebagai sarana untuk mengukur seberapa jauh tingkat pemahaman anda terhadap materi ini.

### 3. Tujuan Pembelajaran

Setelah mempelajari satuan bahasan 1 ini, mahasiswa diharapkan dapat :

- enjelaskan pengertian komputer dan bagian-bagian utamanya.

- enjelaskan perbedaan antara organisasi komputer dengan arsitektur komputer beserta dengan contohnya masing-masing

- enjelaskan struktur utama komputer beserta fungsinya

- enjelaskan struktur utama dari CPU beserta fungsinya

- engetahui fungsi-fungsi operasi komputer

#### 1.1. Komputer

Kemajuan ilmu pengetahuan sebagai bagian dari peradaban manusia, telah menciptakan perubahan besar dalam kehidupan manusia. Perkembangan teknologi telah menghasilkan suatu perangkat alat hitung yang dulunya masih menggunakan mesin sederhana, kini telah menjelma menjadi perangkat teknologi yang luar biasa.

Disinilah peranan ilmu pengetahuan yang senantiasa wajib dikembangkan demi kemaslahatan umat manusia. Allah mewajibkan setiap umat manusia untuk terus belajar dan menggali potensi ilmunya, sebagaimana dijelaskan dalam QS.Al-Alaq/96:1-5.

Terjemahnya: Bacalah dengan (menyebut) nama Tuhanmu yang Menciptakan. Dia telah menciptakan manusia dari segumpal darah. Bacalah, dan Tuhanmulah yang Maha pemurah. Yang mengajar (manusia) dengan perantaran kalam. Dia mengajar kepada manusia apa yang tidak diketahuinya. (Departemen Agama, 2005)

Ayat tersebut menggambarkan bahwa manusia awalnya tidak punya apa-apa, kecuali Allah mengajarkan melalui perantaraan kalam sehingga manusia mengenal teknologi.

Salah satu produk teknologi yang dihasilkan dari kemajuan ilmu pengetahuan adalah komputer. Komputer adalah sebuah mesin hitung elektronik yang secara cepat menerima informasi masukan digital dan mengolah informasi tersebut menurut seperangkat instruksi yang tersimpan dalam komputer tersebut dan menghasilkan keluaran informasi yang dihasilkan setelah diolah. Daftar perintah tersebut dinamakan program komputer dan unit penyimpanannya adalah memori komputer.

Menurut Hartono (1998), ada beberapa definisi tentang komputer yang disajikan oleh beberapa pakar komputer seperti:

Menurut buku *Computer Annual* (Robert H.Blissmer): komputer adalah suatu alat elektronik yang mampu melakukan beberapa tugas berikut: menerima input; memproses input sesuai dengan programnya, menyimpan perintah-perintah dan hasil dari pengolahan; dan menyediakan output dalam bentuk informasi.

Menurut buku *Computer Organization* (V.C.Hamacher, Z.G.Vranezic, S.G.Zaky): Komputer adalah mesin penghitung elektronik yang cepat, dapat menerima informasi input digital, memprosesnya sesuai dengan suatu program yang tersimpan di memorinya *(stored program)*, dan menghasilkan output informasi.

Menurut buku *Introduction to Computer* (Gordon B.Davis): Komputer adalah tipe khusus alat penghitung yang mempunyai sifat tertentu yang pasti.

Menurut buku *Computer Today* (Donald H.Sanders): Komputer adalah sistem elektronik untuk memanipulasi data yang cepat dan tepat serta dirancang dan diorganisasikan supaya secara otomatis menerima dan menyimpan data input, memprosesnya dan menghasilkan output dibawah pengawasan suatu langkah-langkah instruksi-instruksi program yang tersimpan di memori (stored program).

Dalam bentuk yang paling sederhana komputer terdiri dari lima bagian utama yang mempunyai fungsi sendiri-sendiri. Unit-unit tersebut adalah: masukan, memori, aritmetika dan logika, keluaran dan kontrol seperti pada gambar 1.1.

Memori

Gambar 1.1. Unit fungsional dasar pada komputer

Unit masukan menerima informasi yang dikodekan dari operator manusia lewat alat-alat elektromekanik seperti papan ketik pada suatu terminal video, atau dari komputer-komputer lain lewat

jalur komunikasi digital. Informasi yang diterima dan disimpan dalam memori untuk dipergunakan kelak, atau langsung diolah oleh rangkaian aritmetika dan logika untuk melaksanakan operasi yang diinginkan. Langkah-langkah pengolahan ditentukan oleh program yang disimpan dalam memori. Akhirnya hasil-hasil yang diperoleh dikirimkan kembali keluar melalui unit keluaran. Seluruh kegiatan ini dikoordinasi oleh unit kontrol.

#### 1.2. Pengertian Organisasi dan Arsitektur Komputer

Organisasi Komputer adalah bagian yang terkait erat dengan unit—unit operasional dan interkoneksi antar komponen penyusun sistem komputer dalam merealisasikan aspek arsitekturalnya. Contoh aspek organisasional adalah teknologi hardware, perangkat antarmuka, teknologi memori, sistem memori, dan sinyal—sinyal kontrol.

Arsitektur Komputer lebih cenderung pada kajian atribut–atribut sistem komputer yang terkait dengan seorang programmer. Contohnya, set instruksi, aritmetika yang digunakan, teknik pengalamatan, mekanisme I/O.

Sebagai contoh apakah suatu komputer perlu memiliki instruksi pengalamatan tanpa memori merupakan masalah rancangan arsitektural. Apakah instruksi pengalamatan tersebut akan diimplementasikan secara langsung ataukah melalui mekanisme *cache* adalah kajian organisasional.

# 1.3. Struktur dan Fungsi Utama Komputer

## 1.3.1. Struktur Komputer

Komputer adalah sebuah sistem yang berinteraksi dengan cara tertentu dengan dunia luar. Interaksi dengan dunia luar dilakukan melalui perangkat peripheral dan saluran komunikasi. Dalam buku ini akan banyak dikaji seputar struktur internal komputer. Perhatikan gambar 1.2, terdapat empat struktur utama:

- Central Processing Unit (CPU), berfungsi mengendalikan kerja komputer, pemrosesan data dan pusat pengolahan fungsi – fungsi komputer. CPU sering juga disebut sebagai processor (prosesor).

- *Memori Utama*, berfungsi sebagai penyimpan data yang akan atau baru saja diproses.

- *I/O (Input/Output)*, berfungsi memindahkan data antara komputer ke lingkungan luar atau perangkat lainnya.

System Interconnection, yang lebih dikenal dengan istilah bus merupakan mekanisme yang menghubungkan komunikasi internal antara CPU, memori utama dan I/O.

Gambar 1.2. Struktur Dasar Komputer

Salah satu komponen yang paling kompleks dan merupakan 'jantung'nya komputer adalah CPU. Struktur CPU terlihat pada gambar 1.2 dengan struktur utamanya adalah :

- Control Unit, berfungsi untuk mengontrol operasi CPU dan mengontrol komputer secara keseluruhan.

- Arithmetic And Logic Unit (ALU), berfungsi untuk membentuk fungsi– fungsi pengolahan data komputer.

- Register, berfungsi sebagai penyimpan internal bagi CPU.

CPU Interconnection, berfungsi menghubungkan seluruh bagian dari CPU.

## 1.3.2. Fungsi Komputer

Fungsi dasar sistem komputer adalah sederhana seperti terlihat pada gambar 1.3. Pada prinsipnya terdapat empat buah fungsi operasi, yaitu:

a. Fungsi Operasi Pengolahan Data, seperti penjumlahan, pengurangan, konversi terhadap data, dan lain sebagainya,

- b. Fungsi Operasi Penyimpanan Data, seperti penyimpanan data hasil pemrosesan, pengambilan data yang telah disimpan

- c. Fungsi Operasi Pemindahan Data, seperti pergerakan data internal dan pergerakan data eksternal,

- d. Fungsi Operasi Kontrol, berfungsi mengendalikan ketiga fungsi diatas.

Gambar 1.3. Fungsi Dasar Komputer

Komputer harus dapat *memproses data*. Representasi data disini bermacam-macam, akan tetapi nantinya data harus disesuaikan dengan mesin pemrosesnya. Dalam pengolahan data, komputer memerlukan unit penyimpanan sehingga diperlukan suatu mekanisme penyimpanan data. Walaupun hasil komputer digunakan saat itu, setidaknya komputer memerlukan media penyimpanan untuk data prosesnya. Dalam interaksi dengan dunia luar sebagai fungsi pemindahan data diperlukan antarmuka (interface), proses ini dilakukan oleh unit *Input*/Output (I/O) dan perangkatnya disebut *peripheral*. Saat interaksi dengan perpindahan data yang jauh atau dari remote device, komputer melakukan proses komunikasi Gambar mengilustrasikan operasi-operasi komputer. Gambar 1.4a adalah operasi pemindahan data, gambar 1.4b adalah operasi penyimpanan

data, gambar 1.4c adalah operasi pemrosesan data dan gambar 1.4d adalah operasi pengolahan data.

Gambar 1.4. Operasi-operasi komputer

## Rangkuman

- 1. Dalam bentuk yang paling sederhana komputer terdiri dari lima bagian utama yang mempunyai fungsi sendiri-sendiri. Unit-unit tersebut adalah : masukan, memori, aritmetika dan logika, keluaran dan kontrol

- 2. Organisasi Komputer adalah bagian yang terkait erat dengan unit-unit operasional dan interkoneksi antar komponen penyusun sistem komputer dalam merealisasikan aspek arsitekturalnya. Sedangkan

#### Pengantar Organisasi dan Arsitektur Komputer

- Arsitektur Komputer lebih cenderung pada kajian atribut–atribut sistem komputer yang terkait dengan seorang programmer.

- 3. Terdapat 4 struktur utama dalam komputer yaitu : CPU, memori utama, Input/Output, dan System Interkoneksi (sistem bus)

- 4. Terdapat 4 struktur utama dalam CPU yaitu : Control Unit, ALU, Register, dan System Interkoneksi (sistem bus).

- 5. Fungsi dasar komputer meliputi fungsi operasi pengolahan data, penyimpanan data, pemindahan data, dan fungsi control.

#### Tes Formatif

- 1. Jelaskan perbedaan antara pengertian organisasi komputer dengan arsitektur komputer!

- 2. Jelaskan struktur utama dari komputer beserta fungsinya masing-masing!

- 3. Jelaskan pula struktur utama dari CPU beserta fungsinya masing-masing!

- 4. Sebutkan fungsi-fungsi operasi komputer dan berikan contohnya masing-masing!

#### **SATUAN BAHASAN 2**

# EVOLUSI DAN KINERJA KOMPUTER

#### 1. Gambaran Singkat Mengenai Materi Kuliah

Dalam materi kuliah pada satuan bahkomputerasan 2 ini mula-mula akan dibahas tentang sejarah singkat komputer yang terbagi dalam beberapa generasi karena beberapa diantaranya merupakan dasar dari perkembangan komputer saat ini. Kemudian dibahas mengenai bermacam-macam teknik dan strategi yang digunakan untuk mencapai unjuk kerja yang seimbang dan efisien. Terakhir akan dibahas evolusi dua sistem yang sangat penting pada komputer saat ini yaitu Pentium dan Power PC.

## 2. Pedoman Mempelajari Materi

Baca dengan cermat dan teliti materi pada satuan bahasan 2, kemudian pahami setiap bagian dari evolusi komputer. Hal ini akan membantu anda dalam memahami sejarah perkembangan komputer beserta kinerjanya setiap generasi. Pada akhir satuan bahasan terdapat tes formatif yang perlu anda kerjakan sebagai sarana untuk mengukur seberapa jauh tingkat pemahaman anda terhadap materi ini.

## 3. Tujuan Pembelajaran

Setelah mempelajari satuan bahasan 2 ini, mahasiswa diharapkan dapat :

engetahui sejarah perkembangan komputer di setiap generasinya

engetahui jenis-jenis komputer yang dirancang di setiap generasinya

enjelaskan beberapa teknik yang dikembangkan dalam perancangan kinerja komputer

enjelaskan evolusi komputer pada kelompok Intel Pentium dan Power PC

#### 2.1. Sejarah Perkembangan Komputer

Sebagai bagian dari perkembangan teknologi informasi dewasa ini, komputer yang digunakan saat ini tentunya melalui proses evolusi yang panjang. Komputer yang dulunya adalah alat hitung yang sangat sederhana kini menjadi suatu perangkat teknologi yang saat ini memudahkan segala aktifitas manusia. Bahkan dalam kurun waktu lebih dari sepuluh tahun ini, menjelma menjadi perangkat yang mampu menggabungkan berbagai teknologi dalam bentuk laptop, gadget yang sifatnya *mobile* dan lebih dinamis.

Sejarah perkembangan komputer dikelompokkan dalam beberapa generasi. Hal ini bertujuan untuk memudahkan pemahaman tentang perubahan teknologi yang digunakan setiap generasinya. Perubahan teknologi tidak serta merta terjadi begitu saja. Manusia diberi akal dan ilmu untuk terus mengembangkan pengetahuannya dan menghasilkan penemuan-penemuan yang luar biasa. Allah swt telah memberikan ilmu kepada manusia dan melebihkannya dibanding makhluk-makhluk ciptaan lainnya sebagaimana dijelaskan dalam QS.An-Naml/27:15.

Terjemahnya: "dan Sesungguhnya Kami telah memberi ilmu kepada Daud dan Sulaiman; dan keduanya mengucapkan: "Segala puji bagi Allah yang melebihkan Kami dari kebanyakan hamba-hambanya yang beriman".

Ayat tersebut menggambarkan bahwa Allah memberikan ilmu pengetahuan kepada manusia untuk dimanfaatkan dan dikembangkan, sehingga dapat menghasilkan sesuatu yang dapat bermanfaat bagi umat manusia, tentu saja diantaranya teknologi komputer yang sudah kita rasakan manfaatnya saat ini.

# 2.1.1 Komputer Primitif

Pada awalnya cikal bakal komputer dimulai pada tahun 1642 oleh Blaise Pascal yang menciptakan mesin hitung pertama yang

diberi nama Kalkulator Pascal. Kemudian di tahun 1672 ilmuwan Leibniz menambahkan beberapa fungsi lain dan menghasilkan Kalkulator Leibniz.

Sekitar 150 tahun kemudian, seorang professor Matematika dari Universitas Cambridge, Charles Babbage (1791-1871) merancang suatu mesin yang dikenal dengan nama Difference Engine di tahun 1823. Mesin yang dibuat ini masih sangat sederhana dengan menggunakan bahan-bahan mekanik. Mesin ini mampu menghitung tabel matematis.

Sepuluh tahun setelah mesin pertamanya dirancang, tahun 1833 Babbage membuat konsep mesin baru yaitu Analytic Engine. Mesin ini dapat dianggap sebagai konsep awal sebuah komputer serbaguna yang dapat digunakan untuk berbagai tujuan. (Abdurohman, 2014).

Satu dekade berikutnya adalah masa peralihan menuju awal generasi komputer. Perkembangan komputer waktu itu tidak hanya untuk keperluan penelitian, tetapi juga digunakan untuk berbagai kepentingan dalam perang dunia II.

JohnAtanasoff seorang ilmuwan dari Iowa State University, tahun 1930-an merancang sebuah mesin *Linear Equation Solver* (pemecah persamaan linear). Tidak kurang dari 300 buah tabung digunakannya sebagai teknologi dasar pembangun rancangannya ini. Mesin ini mampu menyelesaikan persamaan linear dan integral diferensial.

Atanasoff-Berry Computer (1937-1942) adalah komputer digital pertama yang mengimplementasikan perhitungan biner untuk menyelesaikan persamaa linear. Hampir bersamaan, Konrad Zuse, ilmuwan Jerman merancang Z3 (1941), sebuah komputer elektrikmekanik serbaguna yang dapat diprogram. Di Inggris, Tommy Flowers merancang Colossus (1944), komputer elektronik yang dapat diprogram. Harvard Mark I (1944) dirancang oleh Howard Aiken bekerjasama dengan IBM sejak 1939. Harvar Mark I dikenal juga sebagai IBM ASCC (Automatic Sequence Controlled Calculator), merupakan komputer digital otomatis pertama di Amerika. (Abdurohman, 2014).

# 2.1.2 Generasi Pertama : Tabung Vakum (1945 – 1955) ENIAC

ENIAC (Electronic Numerical Integrator And Computer), pada tahun 1946 dirancang dan dibuat oleh John Mauchly dan John Presper Eckert di Universitas Pennsylvania merupakan komputer digital elektronik untuk kebutuhan umum pertama di dunia. ENIAC dibuat dibawah lembaga Army's Ballistics Research Laboratory (BRL). Sebuah badan yang bertanggungjawab dalam pembuatan jarak dan table lintasan peluru kendali senjata baru. Sebelumnya tugas ini dilakukan oleh kurang lebih 200 personil dengan menggunakan kalkulator untuk menyelesaikan persamaan matematis peluru kendali yang memakan waktu lama.

ENIAC mempunyai berat 30 ton, bervolume 15.000 kaki persegi, dan berisi lebih dari Tabung vakum. Daya listrik yang dibutuhkan sebesar 140KW. Kecepatan operasi mencapai 5.000 operasi penambahan perdetik. ENIAC masih merupakan mesin desimal, representasi data bilangan dalam bentuk decimal dan arimetiknya dibuat dalam bentuk desimal. Memorinya terdiri atas 20 akumulator, yang masing — masing akumulatornya mampu menampung 10 digit desimal. Setiap digit direpresentasikan oleh cincin yang terdiri atas10 buah tabung vakum. Kekurangan utama mesin ini adalah masih manual pemrogramannya, yaitu dengan menyetel switch—switch, memasang dan menanggalkan kabel—kabelnya. ENIAC selesai pada tahun 1946 sejak proposal diajukan tahun 1943, sehingga tahun 1946 merupakan gerbang bagi zaman baru komputer elektronik.

John Van Neumann seorang ahli matematika yang merupakan konsultan pembuatan ENIAC pada tahun 1945 mencoba memperbaiki kelemahan ENIAC dengan rancangan komputer barunya, bernama **EDVAC** ( *Electronic Discrete Variable Computer* ) dengan konsep program tersimpan (*stored-program concept*).

Organisasi & Arsitektur Komputer

### Gambar 2.1. John von Neumann

Tahun 1946 komputer dengan *stored-program concept* dipublikasikan, yang kemudian dikenal dengan Komputer IAS *(Computer of Institute for Advanced Studies).* Struktur komputer IAS terlihat pada gambar 2.2. Komputer ini terdiri:

- Memori Utama, untuk menyimpan data maupun instruksi.

- Arithmetic Logic Unit (ALU), untuk mengolah data binner. Control Unit, untuk melakukan interpretasi instruksi—instruksi di dalam memori sehingga adanya eksekusi instruksi tersebut.

- *I/O*, untuk berinteraksi dengan lingkungan luar.

Gambar 2.2. Struktur Komputer IAS

Memori IAS terdiri atas 1.000 lokasi penyimpanan yang disebut *word*. Word terdiri atas 40 *binary digit* (bit). Data maupun instruksi disimpan dalam memori ini, sehingga data maupun instruksi harus dikodekan dalam bentuk biner. Format memori terlihat pada gambar 2.2. Setiap bilangan terdiri atas sebuah bit tanda dan 39 bit nilai. Sebuah word terdiri atas 20 bit instruksi dengan masing—masing 8 bit kode operasi (*op code*) dan 12 bit alamat.

| Instruksi kiri                   | Instruksi kanan |

|----------------------------------|-----------------|

| Organisasi & Arsitektur Komputer | 13              |

| 0      | 8      | 19 20   | 28       | 39 |

|--------|--------|---------|----------|----|

| OpCode | Alamat | Op Code | e Alamat |    |

Gambar 2.3 Format memori IAS

Struktur detail komputer IAS disajikan dalam gambar 2.3. Gambar ini menjelaskan bahwa baik unit kontrol maupun ALU berisi lokasi–lokasi penyimpanan, yang disebut *register*, yaitu:

- Memory Buffer Register (MBR), berisi sebuah word yang akan disimpan didalam memori atau digunakan untuk menerima word dari memori.

- Memory Address Register (MAR), untuk menentukan alamat word dimemori untuk dituliskan dari MBR atau dibaca oleh MBR.

- Instruction Register (IR), berisi instruksi 8 bit kode operasi yang akan dieksekusi.

- Instruction Buffer Register (IBR), digunakan untuk penyimpanan sementara instruksi sebelah kanan word didalam memori.

- Program Counter (PC), berisi alamat pasangan instruksi berikutnya yang akan diambil dari memori.

- Accumulator (AC) dan Multiplier Quotient (MQ), digunakan untuk penyimpanan sementara operand dan hasil ALU. Misalnya, hasil perkalian 2 buah bilangan 40 bit adalah sebuah bilangan 80 bit; 40 bit yang paling berarti (most significant bit) disimpan dalam AC dan 40 bit lainnya (least significant bit) disimpan dalam MQ.

Organisasi & Arsit

#### Gambar 2.4 Struktur detail komputer IAS

IAS beroperasi secara berulang membentuk siklus instruksi. Komputer IAS memiliki 21 instruksi, yang dapat dikelompokkan seperti berikut ini :

- Data transfer, memindahkan data diantara memori dengan registerregister ALU atau antara dua register ALU sendiri.

- *Unconditional branch*, perintah perintah eksekusi percabangan tanpa syarat tertentu.

- Conditional branch, perintah-perintah eksekusi percabangan yang memerlukan syarat tertentu agar dihasilkan suatu nilai dari percabangan tersebut.

- Arithmetic, kumpulan operasi– operasi yang dibentuk oleh ALU.

- Address Modify, instruksi– instruksi yang memungkinkan pengubahan alamat saat dikomputasi sehingga memungkinkan fleksibilitas alamat yang tinggi pada program.

#### Komputer Komersial

Tahun 1950 dianggap sebagai tahun kelahiran industri komputer dengan munculnya 2 buah perusahaan yang saat itu mendominasi pasar, yaitu Sperry dan IBM.

Tahun 1947, Eckert dan Mauchly mendirikan Eckert-Mauchly Computer Corporation untuk memproduksi komputer secara komersial. Komputer pertama yang mereka hasilkan adalah UNIVAC I (*Universal Automatic Computer*). UNIVAC I menjadi tulang punggung penghitungan sensus tahun 1950 di USA.

UNIVAC II yang memiliki kapasitas memori lebih besar dan kinerja yang lebih baik diluncurkan tahun 1950. Mulai saat itu perusahaan telah mengembangkan produk–produk baru yang kompatibel dengan produk sebelumnya sehingga pangsa pasar konsumen mereka tetap terjaga menggunakan produknya.

IBM pun tidak mau kalah dengan mengeluarkan produk mereka yang akhirnya mendominasi pangsa pasar bisnis saat ini. Seri IBM pertama adalah seri 701 tahun 1953 dan terus berkembang menjadi lebih baik hingga sekarang.

# 2.1.3 Generasi Kedua : Transistor (1955 – 1965)

Sejak pesatnya teknologi semi konduktor hingga menghasilkan komponen transistor membawa perubahan besar pada dunia

komputer. Komputer era ini tidak lagi menggunakan tabung vakum yang memerlukan daya operasional besar, tabung–tabung itu digantikan komponen kecil bernama transistor. Konsumsi daya listrik amat kecil dan bentuknya pun relatif kecil.

Transistor ditemukan di Bell Labs pada tahun 1947 dan tahun 1950 telah meluncurkan revolusi elektronika modern. IBM sebagai perusahaan pertama yang meluncurkan produk komputer dengan transistor sehingga tetap mendominasi pangsa pasar komputer. NCR dan RCA adalah perusahaan yang mengembangkan komputer berukuran kecil saat itu, kemudian diikuti IBM dengan mengeluarkan seri 7000-nya.

Dengan adanya transistor membuat hardware komputer saat itu makin cepat prosesnya. Memori makin besar kapasitasnya namun makin kecil bentuknya. Generasi dua ini juga terdapat perubahan perkembangan pada ALU yang makin kompleks, lahirnya bahasa pemrograman tingkat tinggi maupun tersedianya software sistem operasi.

Generasi kedua juga ditandai munculnya *Digital Equipment Corporation* (DEC) tahun 1957 dan meluncurkan komputer pertamanya, yaitu PDP-1. Komputer ini sangat penting bagi perkembangan komputer generasi ketiga.

#### **IBM 7094**

Komputer ini diluncurkan tahun 1962. Kemajuan IBM 7094 adalah adanya *Instruction Backup Register* ( IBR ) yang berfungsi membeffer instruksi berikutnya, efeknya komputer akan lebih cepat prosesnya. Unit control mengambil dua word yang berdampingan dari memori untuk sebuah pengambilan instruksi, kecuali bila terjadi percabangan.

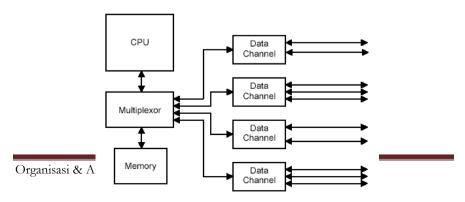

Kemajuan IBM 7094 lainnya adalah adanya *multiplexor* untuk memultiplex *data channel* (saluran data). Multiplexor berfungsi sebagai sentral switch data yang akan diproses dalam CPU. Gambar 2.5 merupakan konfigurasi IMB 7094.

## Gambar 2.5 Konfigurasi IBM 7094

#### 2.1.4 Generasi Ketiga: Integrated Circuits (1965 – 1980)

Pada tahun 1958 terjadi revolusi elektronika kembali, yaitu ditemukannya *integrated circuit* (IC) yang merupakan penggabungan komponen–komponen elektronika dalam suatu paket. Dengan ditemukan IC ini semakin mempercepat proses komputer, kapasitas memori makin besar dan bentuknya semakin kecil.

#### IBM System/360

Tahun 1964 dikeluarkan IBM System/360 yang telah menggunakan teknologi IC. Dalam satu decade IBM menguasai 70% pasaran komputer.

Sistem 360 merupakan kelompok komputer pertama yang terencana. Banyak model dalam arsitektur 360 ini dan saling kompatibel. Hal ini sangat menguntungkan konsumen, karena konsumen dapat menyesuaikan dengan kebutuhan maupun harganya. Pengembangan (*upgrading*) dimungkinkan dalam komputer ini. Karakteristik komputer kelompok ini adalah:

- Set Instruksi Mirip atau Identik, dalam kelompok komputer ini berbagai model yang dikeluarkan menggunakan setinstruksi yang sama sehingga mendukung kompabilitas sistem maupun perangkat kerasnya.

- Sistem Operasi Mirip atau Identik, ini merupakan feature yang menguntungkan konsumen sehingga apabila kebutuhan menuntut penggantian komputer tidak kesulitan dalam sistem operasinya karena sama.

- Kecepatan yang meningkat, model—model yang ditawarkan mulai dari kecepatan rendah sampai kecepatan tinggi untuk penggunaan yang dapat disesuaikan konsumen sendiri.

- *Ukuran Memori yang lebih besar*, semakin tinggi modelnya akan diperoleh semakin besar memori yang digunakan.

- Harga yang meningkat, semakin tinggi modelnya maka harganya semakin mahal.

Tabel 2.1 Karakteristik Penting Kelompok Sistem /360

| Karakteristik     | Model | Model | Model | Model | Model |

|-------------------|-------|-------|-------|-------|-------|

| Ukuran memori(Kb) | 64    | 256   | 256   | 512   | 512   |

| Laju data dari memori       | 0.5 | 0.8   | 2.0 | 8.0  | 16.0 |

|-----------------------------|-----|-------|-----|------|------|

| Prosesor cycle time(µdetik) | 1.0 | 0.625 | 0.5 | 0.25 | 0.2  |

| Jumlah maksimum data        | 3   | 3     | 4   | 6    | 6    |

| Data maks per               | 250 | 400   | 800 | 1250 | 1250 |

#### **DEC PDP-8**

Pada tahun yang sama saat IBM mengeluarkan System /360, DEC meluncurkan DEC PDP-8. Komputer ini memiliki keunggulan bentuknya yang kecil sehingga sangat fleksibel digunakan.

PDP-8 juga memiliki varian-varian yang modelnya sama dengan IBM System/360 untuk menyesuaikan kebutuhan pelanggannya. Dengan hadirnya PDP-8 ini membawa DEC sebagai perusahaan menyuplai komputer mini terbesar membawa DEC sebagai pabrik komputer terbesar kedua setelah IBM.

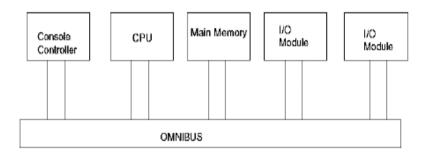

Arsitektur PDP-8 sangat berbeda dengan IBM terutama bagian sistem bus. Pada komputer ini menggunakan omni bus system. Sistem ini terdiri atas 96 buah lintasan sinyal yang terpisah, yang digunakan untuk membawa sinyal—sinyal kontrol, alamat maupun data. Karena semua komponen menggunakan jalur bus ini maka penggunaannya dikontrol oleh CPU. Arsitektur bus seperti PDP-8 ini nantinya digunakan oleh komputer—komputer modern selanjutnya. Struktur bus PDP-8 terlihat pada gambar 2.6.

Gambar 2.6. Struktur Bus PDP-8

# 2.1.5 Generasi Keempat : Very Large Scale Integration (1980 - sekarang)

Era keempat perkembangan generasi komputer ditandai adanya VLSI. Paket VLSI dapat menampung 10.000 komponen lebih perkepingnya dengan kecepatan operasi mencapai 100 juta operasi

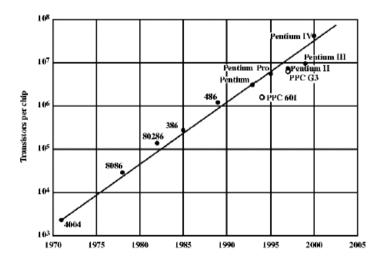

perdetiknya. Gambar 2.7 mengilustrasikan perkembangan mikroprosesor Pentium terhadap jumlah transistor per kepingnya. Masa–masa ini diawali peluncuran mikroprosesor Intel seri 4004.

Mikroprosesor 4004 dapat menambahkan dua bilangan 4 bit dan hanya dapat mengalikan dengan cara pengulangan penambahan. Memang masih primitif, namun mikroprosesor ini tonggak perkembangan mikroprosesor—mikroprosesor canggih saat ini. Tidak ada ukuran pasti dalam melihat mikroprosesor, namun ukuran terbaik adalah *lebarbus data*: jumlah bit data yang dapat dikirim—diterima mikroprosesor. Ukuran lain adalah *jumlah bit dalam register*.

Tahun 1972 diperkenalkan dengan mikroprosesor 8008 yang merupakan mikroprosesor 8 bit. Mikroprosesor ini lebih kompleks instruksinya tetapi lebih cepat prosesnya dari pendahulunya. Kemudian Bells dan HP menciptakan mikroprosesor 32 bit pada 1981, sedangkan Intel baru mengeluarkan tahun 1985 dengan mikroprosesor 80386.

Gambar 2.7 Grafik jumlah transistor dalam chips Pentium

# 2.2 Perancangan Kinerja

Kinerja sebuah sistem komputer merupakan hasil proses dari seluruh komponen komputer, yang melibatkan CPU, memori utama, memori sekunder, bus, peripheral. Dari segi perkembangan program aplikasi pun sangat menakjubkan. Aplikasi desktop yang hampir dimiliki semua sistem komputer saat ini meliputi :

- Pengolahan citra

- Pengenalan voice atau pembicaraan

- Video conference

- Mulitimedia

- Transfer data

Yang menakjubkan lagi adalah dari sudut pandang organisasi dan arsitektur komputer saat ini adalah mirip dengan komputer IAS yang dibuat sekitar 50 tahun lalu, namun perkembangan dan kecanggihannya dapat kita rasakan sekarang ini. Peningkatan kinerja mikroprosesor ini terus berlanjut tidak kenal henti dengan berbagai teknik yang telah dikembangkan, diantaranya:

- Branch Prediction, teknik dimana prosesor memungkinkan mengamati terlebih dahulu didalam software dan melakukan prediksi percabangan atau kelompok instruksi yang akan dieksekusi berikutnya.

- Data Flow Analysis, prosesor akan menganalisa instruksi– instruksi yang tidak tergantung pada hasil atau data lainnya untuk membuat penjadwalan yang optimum dalam eksekusi.

- Speculative Execution, dengan modal prediksi cabang dan analisis data, maka prosesor dapat melakukan eksekusis pekulatif terlebih dahulu sebelum waktunya.

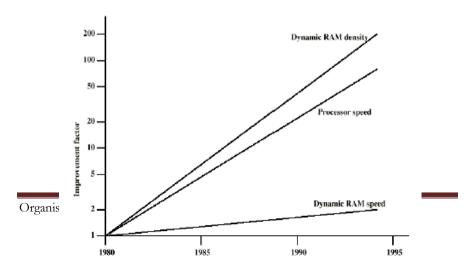

Perkembangan mikroprosesor, dilihat dari kapasitas operasi dan kecepatannya sangatlah pesat. Perkembangan mikroprosesor ini sulit diimbangi oleh komponen lainnya semisal memori. Hal ini menimbulkan masalah kesenjangan dan kurang sinkronnya operasi antar komponen. Perhatikan laju perkembangan prosesor dibandingkan memori utama seperti terlihat pada gambar 2.8. Organisasi dan arsitektur komputer yang handal sangat diperlukan untuk mengatasi persoalan seperti ini.

# Gambar 2.8 Grafik perbandingan kecepatan mikroprosesor dan memori

Terdapat beberapa metode untuk mengatasi masalah perbedaan kecepatan operasi antara mikroprosesor dengan komponen lainnya, diantaranya:

- Meningkatkan jumlah bit yang dicari pada suatu saat tertentu dengan melebarkan DRAM dan melebarkan lintasa system busnya.

- Mengubah antar muka DRAM sehingga lebih efisien dengan menggunakan teknik cache atau pola buffer lainnya pada keeping DRAM.

- Meningkatkan bandwidth inter koneksi prosesor dan memori dengan penggunakan hierarki bus—bus yang lebih cepat untuk buffering dan membuat struktur aliran data.

Bidang lain yang menjadi fokus kajian peningkatan kinerja sistem komputer adalah penanganan perangkat— perangkat I/O. Masalah yang terjadi hampir sama dengan memori. Teknik penyelesaian yang digunakan umumnya adalah teknik *buffering* dan *caching*.

Target yang ingin dicapai dalam peningkatan kinerja adalah tercapainya keseimbangan proses operasi antar komponen–komponen penyusun komputer sehingga menghasilkan kinerja komputer yang tinggi.

## 2.3 Contoh Evolusi Komputer

Evolusi komputer yang akan dijelaskan adalah kelompok komputer Pentium Intel dan Power PC. Alasannya adalah komputer Pentium Intel mampu mendominasi pasaran dan secara teknologi menggunakan rancangan CISC (complex instruction set computers) dalam arsitekturnya. Sedangkan Power PC merupakan kelompok komputer yang menerapkan teknologi RISC (reduced instruction set computers).

#### Pentium

Pentium merupakan produk Intel yang mampu mendominasi pasaran prosesor hingga saat ini. Generasi demi generasi diluncurkan kepasaran dengan kenaikan unjuk kerja yang menakjubkan dalam memenuhi kebutuhan konsumennya.

Berikut evolusi prosesor keluaran Intel dari prosesor sederhana sampai prosesor keluaran saat ini :

- Intel 4004, yang dikeluarkan pada tahun 1971 merupakan mikroproseseor pertama di dunia. Lebar bus data 4 bit, no interrupt dan jumlah pin 16 pin DIP.

- Intel 4040, dengan lebar bus data 4 bit, no interrupt dan jumlah pin 24 pin DIP.

- Intel 8008, dikeluarkan tahun 1972 merupakan mikroprosesor 8-bit pertama yang mampu melaksanakan 48 instruksi dengan ukuran memori 16 KB. Adanya instruksi tambahan menyebabkan prosesor ini dapat diaplikasikan dalam sejumlah aplikasi yang lebih maju.

- Intel 8080, keluar tahun 1973 merupakan mikroprosesor modern pertama keluaran Intel dengan mesin 8 bit dan bus data ke memori juga 8bit. Jumlah instruksinya 66 instruksi dengan kemampuan pengalamatan 16KB. Dapat melaksanakan instruksi 10 kali lebih cepat dari 8008.

- 8086, dikenalkan tahun 1974 adalah mikroprosesor 16 bit dengan teknologi cache instruksi. Jumlah instruksi mencapai 111 dan kemampuan pengalamatan ke memori 64KB.

- 80286, keluar tahun 1982 merupakan pengembangan dari 8086, kemampuan pengalamatan mencapai 1MB dengan 133 instruksi.

- 80386, keluar tahun 1985 dengan mesin 32 bit. Sudah mendukung sistem multi tasking. Dengan mesin 32 bitnya, produk ini mampu menjadi terunggul pada masa itu.

- 80486, dikenalkan tahun 1989. Kemajuannya pada teknologi *cache* memori dan *pipelining* instruksi. Sudah dilengkapi dengan *math co-processor*.

- Pentium, dikeluarkan tahun 1993, menggunakan teknologi *superscalar* sehingga memungkinkan eksekusi instruksi secara paralel.

- Pentium Pro, keluar tahun 1995. Kemajuannya pada peningkatan organisasi *superscalar* untuk proses paralel, ditemukan sistem prediksi cabang, analisa aliran data dan sistem cache memori yang makin canggih.

- Pentium II, keluar sekitar tahun 1997 dengan teknologi MMX sehingga mampu menangani kebutuhan multimedia. Mulai Pentium II telah menggunakan teknologi RISC.

- Pentium III, terdapat kemampuan instruksi *floating point* untuk menangani grafis 3D.

- Pentium IV, diproduksi tahun 2000 merupakan produk Intel yang kecepatan prosesnya mampu menembus kecepatan hingga 3,06 GHz.

- Itanium, memiliki kemampuan 2 unit floating point, 4 unit integer, 3 unit pencabangan, internet streaming, 128 interger register.

- Intel Core 2 Duo dibangun di beberapa fasilitas manufaktur bervolume tinggi dan canggih di dunia menggunakan proses berteknologi silikon 64-nanometer dari Intel. Intel Corporation meluncurkan prosesor Intel Core 2 Duo yang ditujukan bagi PC dan workstation desktop dan laptop consumer dan bisnis prosesor dengan teknologi yang dapat menghasilkan kinerja lebih, konsumsi daya lebih kecil, serta keleluasaan pemakaian bagi para penggunanya.

- Întel Core i3, i5, dan i7, merupakan seri prosesor yang dikeluarkan oleh Intel dan saat ini banyak digunakan pada laptop maupun desktop.

#### **PowerPC**

Proyek sistem RISC diawali tahun 1975 oleh IBM pada komputer mini seri 801. Seri pertama ini hanyalah prototipe, seri komersialnya adalah PCRT yang dikenalkan tahun 1986. Tahun 1990 IBM mengeluarkan generasi berikutnya yaitu IBMRISC System /6000 yang merupakan mesin RISC super scalar work station. Setelah ini arsitektur IBM lebih dikenal sebagai arsitektur POWER.

IBM menjalin kerjasama dengan Motorola menghasilkan mikroprosesor seri 6800, kemudian Apple menggunakan keeping Motorola dalam Macintoshnya. Saat ini terdapat 4 kelompok Power PC, yaitu:

- 601, adalah mesin 32 bit merupakan produksi masal arsitektur Power PC untuk lebih dikenal masyarakat.

- 603, merupakan komputer desktop dan komputer portabel. Kelompok ini sama dengan seri 601 namun lebih murah untuk keperluan efisien.

- 604, seri komputer Power PC untuk kegunaan komputer *low-end* server dan komputer desktop.

- 620, ditujukan untuk penggunaan *high-end server*. Mesin dengan arsitektur 64 bit.

- •740/750, seri dengan cache L2.

- •G4, seperti seri 750 tetapi lebih cepat dan menggunakan 8 instruksi parallel

## Rangkuman

1. Sejarah perkembangan komputer dapat dikelompokkan dalam beberapa generasi berdasarkan teknologi yang digunakan.

#### Evolusi dan Kinerja Komputer

- 2. ENIAC merupakan komputer digital elektronik untuk kebutuhan umum pertama di dunia.

- 3. Tahun 1946 komputer dengan konsep stored program concept dipublikasikan yang kemudian dikenal dengan komputer IAS (Computer of Institute for Advance Studies). Merupakan komputer yang menjadi pondasi sistem komputer modern yang digunakan saat ini.

#### **Tes Formatif**

- 1. Jelaskan secara umum perkembangan komputer ENIAC!

- 2. Mengapa John von Neumann dianggap sebagai peletak dasar sistem komputer modern!

- 3. Jelaskan struktur utama dari komputer IAS!

- 4. Jelaskan teknik-teknik yang dikembangkan dalam perancangan kinerja komputer!

#### **SATUAN BAHASAN 4**

# GERBANG LOGIKA DASAR & ALJABAR BOOLEAN

## 1. Gambaran Singkat Mengenai Materi Kuliah

Materi kuliah dari satuan bahasan yang pertama ini berisikan tentang pengertian dari komputer, perbedaan antara organisasi dengan arsitektur komputer. Juga membahas tentang fungsi dan struktur dasar dari komputer.

## 2. Pedoman Mempelajari Materi

Baca dengan cermat dan teliti materi pada satuan bahasan 4, kemudian pahami setiap teori yang akan membantu pemahaman anda tentang organisasi dan arsitektur komputer itu sendiri. Pada akhir satuan bahasan terdapat tes formatif yang perlu anda kerjakan sebagai sarana untuk mengukur seberapa jauh tingkat pemahaman anda terhadap materi ini.

# 3. Tujuan Pembelajaran

Setelah mempelajari satuan bahasan 4 ini, mahasiswa diharapkan dapat :

- enjelaskan pengertian tabel kebenaran dan

- enjelaskan sifat dan karakteristik macam-macam gerbang logika

- engetahui teorema-teorema Aljabar Boole, baik teorema variabel tunggal maupun teorema variabel jamak

- enghubungkan keterkaitan antara gerbang logika dengan tabel kebenaran.

- engimplementasikan persamaan logika dalam bentuk rangkaian logika

### 4.1. Tabel Kebenaran (Truth Table)

Tabel kebenaran merupakan tabel yang menunjukkan pengaruh pemberian level logika pada input suatu rangkaian logika terhadap keadaan level logika outputnya. Melalui tabel kebenaran dapat diketahui watak atau karakteristik suatu rangkaian logika. Oleh karena itu, tabel kebenaran mencerminkan watak atau karakteristik suatu rangkaian logika. Sebagaimana manusia harus memiliki watak dan karakteristik untuk mempergunakan ilmu pengetahuannya ke jalan yang diridhai oleh Allah swt.

Berbicara mengenai ilmu, Allah swt dalam QS. Al 'Ankabuut/29:43:

Terjemahannya: "Dan perumpamaan-perumpamaan ini Kami buat untuk manusia; dan tiada yang memahaminya kecuali orang-orang yang berilmu" (Departemen Agama RI,2005).

Makna ayat tersebut diatas adalah, Allah swt mengumpamakan sesuatu perumpamaan bagi manusia. Hanya orang berakal yang dapat memikirkan perumpamaan tersebut. Allah swt mengambil laba-laba sebagai perumpamaan, untuk memudahkan manusia untuk memahaminya. Selain dari itu, juga dimaksudkan untuk menerangkan segala keraguan mereka selama ini. Bagi orang yang selalu menggunakan hati dan pikirannya dan bagi ahli-ahli ilmu pengetahuan, pasti dapat memahami perumpamaan seperti tersebut dan akan semakin banyak mengetahui rahasia-rahasia Allah swt yang terkandung dalam ayat-ayat-Nya.

Dengan adanya ilmu, manusia dapat menemukan kebenaran dan rahasia alam semesta yang diciptakan oleh Allah swt. Seperti yang telah ditulis di atas, bahwa terdapat banyak jalan untuk menemukan kebenaran. Untuk menentukan proses penelusuran kebenaran tadi digunakanlah metodologi.

Tabel kebenaran harus memuat seluruh kemungkinan keadaan input tergantung pada jumlah variabel input atau jumlah saluran input dari suatu rangkaian logika, dan mengikuti rumus :

Jumlah seluruh kemungkinan input = 2<sup>n</sup>, dengan n merupakan jumlah variabel atau saluran input rangkaian .

Contoh:

1. Rangkaian logika dengan 1 variabel input, maka jumlah seluruh kemungkinan input  $= 2^1 = 2$

Gambar 4.1. Diagram blok rangkaian logika satu variabel input Tabel kebenaran:

Tabel 4.1. Tabel kebenaran rangkaian logika satu variabel input

| Input (A) | Output (F) |

|-----------|------------|

| 0         |            |

| 1         |            |

2. Rangkaian logika dengan 2 variabel input, maka jumlah seluruh kemungkinan input =  $2^2 = 4$

Gambar 4.2. Diagram blok rangkaian logika dua variabel input Tabel kebenaran:

Tabel 4.2. Tabel kebenaran rangkaian logika dua variabel input

| In | Output |  |

|----|--------|--|

| A  | F      |  |

| 0  | 0      |  |

| 0 | 1 |  |

|---|---|--|

| 1 | 0 |  |

| 1 | 1 |  |

3. Rangkaian logika dengan 3 variabel input, maka jumlah seluruh kemungkinan input =  $2^3 = 8$

Gambar 4.3. Diagram blok rangkaian logika tiga variabel input Tabel kebenaran:

Tabel 4.3. Tabel kebenaran rangkaian logika tiga variabel input

|   | Output |   |      |

|---|--------|---|------|

| A | В      | С | F    |

| 0 | 0      | 0 | •••• |

| 0 | 0      | 1 | •••• |

| 0 | 1      | 0 |      |

| 0 | 1      | 1 | •••• |

| 1 | 0      | 0 |      |

| 1 | 0      | 1 |      |

| 1 | 1      | 0 |      |

| 1 | 1      | 1 | •••• |

# 4.2. Gerbang Logika Dasar

Gerbang-gerbang dasar logika merupakan elemen rangkaian digital dan rangkaian digital merupakan kesatuan dari gerbang-gerbang logika dasar yang membentuk fungsi pemrosesan sinyal digital. Gerbang dasar logika terdiri dari 3 gerbang utama, yaitu AND Gate,

OR Gate, dan NOT Gate. Gerbang lainnya seperti NAND Gate, NOR Gate, EX-OR Gate dan EX-NOR Gate merupakan kombinasi dari 3 gerbang logika utama tersebut.

#### 4.2.1. AND Gate

Gerbang AND merupakan salah satu gerbang logika dasar yang memiliki 2 buah saluran masukan (input) atau lebih dan sebuah saluran keluaran (output). Suatu gerbang AND akan menghasilkan sebuah keluaran biner tergantung dari kondisi masukan dan fungsinya. Prinsip kerja dari gerbang AND adalah kondisi keluaran (output) akan berlogic 1 bila semua saluran masukan (input) berlogic 1. Selain itu output akan berlogic 0. Simbol gerbang logika AND 2 input :

Gambar 4.4. Simbol Gerbang AND

dengan persamaan Boolean fungsi AND adalah F = A.B (dibaca F = A AND B).

#### Tabel kebenaran:

Tabel 4.4. Tabel kebenaran gerbang AND 2 input

| in | Output |   |  |  |

|----|--------|---|--|--|

| A  | A B    |   |  |  |

| 0  | 0      |   |  |  |

| 0  | 0      |   |  |  |

| 1  | 0      | 0 |  |  |

| 1  | 1      | 1 |  |  |

### 4.2.2. OR Gate

Gerbang OR merupakan salah satu gerbang logika dasar yang memiliki 2 buah saluran masukan (input) atau lebih dan sebuah saluran

keluaran (output). Berapapun jumlah saluran masukan yang dimiliki oleh sebuah gerbang OR, maka tetap memiliki prinsip kerja yang sama dimana kondisi keluarannya akan berlogic 1 bila salah satu atau semua saluran masukannya berlogic 1. Selain itu output berlogic 0. Simbol gerbang logika OR 2 input:

Gambar 4.5. Simbol Gerbang OR

dengan persamaan Boolean fungsi OR adalah F = A+B (dibaca F = A OR B).

#### Tabel kebenaran:

| inp | Output |   |

|-----|--------|---|

| A   | F      |   |

| 0   | 0      |   |

| 0   | 1      |   |

| 1   | 0      | 1 |

1

1

Tabel 4.5. Tabel kebenaran Gerbang OR 2 input

#### 4.2.3. **NOT** Gate

Gerbang NOT sering disebut dengan gerbang inverter. Gerbang ini merupakan gerbang logika yang paling mudah diingat. Gerbang NOT memiliki 1 buah saluran masukan (input) dan 1 buah saluran keluaran (output). Gerbang NOT akan selalu menghasilkan nilai logika yang berlawanan dengan kondisi logika pada saluran masukannya. Bila pada saluran masukannya berlogic 1 maka pada saluran keluarannya akan berlogic 0 dan sebaliknya. Simbol gerbang logika NOT:

1

Gambar 4.6. Simbol Gerbang NOT

Tabel kebenaran:

Tabel 4.6. Tabel kebenaran Gerbang NOT 2 input

| Input (A) | Output (F) |

|-----------|------------|

| 0         | 1          |

| 1         | 0          |

### 4.2.4. NAND Gate

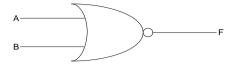

Gerbang NAND merupakan kombinasi dari gerbang AND dengan gerbang NOT dimana keluaran gerbang AND dihubungkan ke saluran masukan dari gerbang NOT. Karena keluaran dari gerbang AND di"NOT"kan maka prinsip kerja dari gerbang NAND merupakan kebalikan dari gerbang AND. Outputnya merupakan komplemen atau kebalikan dari gerbang AND, yakni memberikan keadaan level logic 0 pada outputnya jika dan hanya jika keadaan semua inputnya berlogika 1. Simbol gerbang logika NAND 2 input:

Gambar 4.7. Simbol Gerbang NAND

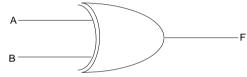

#### 4.2.5. NOR Gate

Sama halnya dengan NAND Gate, gerbang NOR merupakan kombinasi dari gerbang OR dengan gerbang NOT dimana keluaran gerbang OR dihubungkan ke saluran masukan dari gerbang NOT. Karena keluaran dari gerbang OR di"NOT"kan maka prinsip kerja dari gerbang NOR merupakan kebalikan dari gerbang OR. Outputnya merupakan komplemen atau kebalikan dari gerbang OR, yakni memberikan keadaan level logic 0 pada outputnya jika salah satu atau lebih inputnya berlogika 1. Simbol gerbang logika NOR 2 input:

Gambar 4.8. Simbol Gerbang NOR

#### 4.2.6. EX-OR Gate

EX-OR singkatan dari Exclusive OR dimana jika input berlogic sama maka output akan berlogic 0 dan sebaliknya jika input berlogic beda maka output akan berlogic 1. Simbol gerbang logika EX-OR 2 input :

Gambar 4.9. Simbol Gerbang EXOR

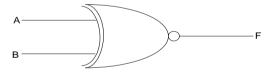

#### 4.2.7. EX-NOR

EX-NOR gate adalah kebalikan dari EX-OR gate dimana jika input berlogic sama maka output akan berlogic 1 dan sebaliknya jika input berlogic beda maka output akan berlogic 0. Simbol gerbang logika EX-NOR 2 input :

Gambar 4.10. Simbol Gerbang EX-NOR

# 4.3. Teorema-teorema Aljabar Boole

Aljabar Boole sangat penting peranannya di dalam proses perancangan maupun analisis rangkaian logika. Untuk memperoleh hasil rancangan yang berupa persamaan logika yang siap diimplementasikan, diperlukan tahap pemberlakuan kaidah-kaidah perancangan. Salah satu alat yang diperlukan di dalam tahap pemberlakuan kaidah-kaidah perancangan adalah aljabar Boole. Demikian juga untuk proses analisis rangkaian logika, aljabar Boole juga diperlukan sebagai alat untuk mengevaluasi output rangkaian

logika. Terdapat dua jenis teorema dalam aljabar Boole yaitu teorema variabel tunggal dan teorema variabel jamak. Masing-masing teorema tersebut memiliki teorema rangkapnya.

## 4.3.1. Teorema Variabel Tunggal

Teorema variabel tunggal aljabar Boole diturunkan dari operasi logika dasar OR, AND dan NOT. Teorema pada operasi AND dapat diperoleh melalui teorema pada operasi OR dan sebaliknya. Untuk memperoleh suatu teorema dari teorema yang diketahui, dapat dilakukan dengan cara:

- a. mengubah tanda + menjadi dot (.) atau sebaliknya

- b. mengubah 1 menjadi 0 atau sebaliknya

Berdasarkan dengan cara tersebut diatas, dapat diambil contoh misalnya terdapat teorema (1): A+1=1, maka menghasilkan teorema (2): A.0=0.

Dari penjelasan diatas dapat dituliskan teorema-teorema aljabar Boole untuk variabel tunggal seperti tersaji pada tabel 4.7 berikut ini.

Tabel 4.7. Teorema-teorema Aljabar Boole untuk variabel tunggal

| Teorema      | Ekspresi                                   | Sifat Rangkap      |

|--------------|--------------------------------------------|--------------------|

| Satu dan Nol | Teorema (1): A+1=1                         | Teorema (2): A.0=0 |

| Identitas    | Teorema (3): A+0=A                         | Teorema (4): A.1=A |

| Idempoten    | Teorema (5): A+A=A                         | Teorema (6): A.A=A |

| Komplemen    | Teorema (7): $A + \overline{A} = 1$        | Teorema (8): A.A=0 |

| Involusi     | Teorema (9): $\overline{\overline{A}} = A$ |                    |

# 4.3.2. Teorema Variabel Jamak

Teorema-teorema variabel jamak aljabar Boole umumnya sama dengan teorema-teorema pada aljabar biasa. Seperti pada aljabar biasa, pada aljabar Boole juga terdapat teori komutatif, asosiatif, dan distributif. Tabel 4.8 berikut menunjukkan teorema-teorema variabel jamak pada aljabar Boole.

Tabel 4.8. Teorema-teorema Aljabar Boole untuk variabel jamak

| Teorema | Ekspresi | Sifat Rangkap |

|---------|----------|---------------|

|         |          |               |

| Komutatif   | Teorema (10):               | Teorema (11):          |

|-------------|-----------------------------|------------------------|

|             | A+B=B+A                     | AB=BA                  |

| Asosiatif   | Teorema (12):               | Teorema (13):          |

|             | A+(B+C)=(A+B)+C             | A(BC)=(AB)C            |

| Distributif | Teorema (14):               | Teorema (15):          |

|             | A+BC=(A+B)(A+C)             | A(B+C)=AB+AC           |

|             | Teorema (16):               | Teorema (17):          |

| Absorpsi    | A + AB = A                  | A(A+B)=A               |

| Absorpsi    | Teorema (18):               | Teorema (19):          |

|             | $A + \overline{AB} = A + B$ | $A(\overline{A}+B)=AB$ |

|             | Teorema (20):               | Teorema (21):          |

| De Morgan   |                             |                        |

|             | $A+B+ = A \cdot B \cdot$    | A.B=A + B +            |

## Rangkuman

- 1. Tabel kebenaran merupakan tabel yang menunjukkan pengaruh pemberian level logika pada input suatu rangkaian logika terhadap keadaan level logika outputnya. Melalui tabel kebenaran dapat diketahui watak atau karakteristik suatu rangkaian logika.

- 2. Ada 3 gerbang logika dasar, yaitu gerbang AND, gerbang OR dan gerbang NOT.

- 3. Gerbang AND (AND gate) didefinisikan sebagai gerbang logika yang memberikan keadaan level logika 1 (tinggi) pada outputnya, jika dan hanya jika semua keadaan inputnya berlevel logika 1 (tinggi).

- 4. Gerbang OR (OR gate) didefinisikan sebagai gerbang logika yang memberikan keadaan level logika 1 (tinggi) pada outputnya, keadaan salah satu atau lebih inputnya berlogika 1 (tinggi).

- 5. Gerbang NOT (NOT gate) merupakan gerbang logika yang memberikan keadaan level logika 1 (tinggi) pada outputnya, jika keadaan inputnya berlogika 1 (rendah) atau sebaliknya gerbang ini akan memberikan keadaan level logika 0 (rendah) pada outputnya jika keadaan inputnya berlevel 1 (tinggi).

- 6. Aljabar Boole sangat penting peranannya di dalam proses perancangan maupun analisis rangkaian logika. Terdapat dua jenis teorema dalam aljabar Boole yaitu teorema variabel tunggal dan teorema variabel jamak.

### Tes Formatif

- 1. Susun tabel kebenaran rangkaian logika dengan tiga input yakni A(MSB), B, dan C(LSB) dan satu output yakni Y yang memberikan keadaan output bernilai tinggi jika:

- a. Input A dan input B berbeda

- b. Input A dan C sama

- c. Input B dan C berbeda

- 2. Implementasikan persamaan berikut ini ke dalam bentuk rangkaian logika!

a.

$$X = (A+B)(A+\overline{C})B$$

b.  $Y = AB\overline{C} + \overline{ABC} + B\overline{C}$

c.  $Z = (A+D) \cdot (B+C)$

#### SATUAN BAHASAN 5

### RANGKAIAN LOGIKA KOMBINASI

### 1. Gambaran Singkat Mengenai Materi Kuliah

Materi kuliah dari satuan bahasan yang kelima ini berisikan tentang pengertian logika kombinasi, bentuk-bentuk persamaan logika (SOP dan POS), dan bagaimana menyederhanakan suatu persamaan logika secara aljabar dengan menggunakan beberapa metode.

## 2. Pedoman Mempelajari Materi

Baca dengan cermat dan teliti materi pada satuan bahasan 5, kemudian pahami setiap teori yang akan membantu pemahaman anda tentang organisasi dan arsitektur komputer itu sendiri. Pada akhir satuan bahasan terdapat tes formatif yang perlu anda kerjakan sebagai sarana untuk mengukur seberapa jauh tingkat pemahaman anda terhadap materi ini.

# 3. Tujuan Pembelajaran

Setelah mempelajari satuan bahasan 5 ini, mahasiswa diharapkan dapat :

- enjelaskan pengertian logika kombinasi.

- engetahui cara mengubah suatu persamaan logika dalam bentuk Sum of Product dan Product of Sum.

- engubah fungsi persamaan logika bentuk tidak standar menjadi bentuk standar

- elakukan penyederhanaan persamaan logika secara aljabar menggunakan metode Aljabar Boolean, Diagram Venn, Karnaugh Map, dan Quinne-Mc.Cluskey

## 5.1. Pengertian Logika Kombinasi

Logika kombinasi merupakan rangkaian logika yang outputnya hanya tergantung pada kombinasi input-inputnya saja, dan tidak tergantung pada keadaan output sebelumnya. Karena kondisi tersebut diatas, logika kombinasi disebut juga rangkaian logika yang outputnya tidak tergantung pada waktu.

Gambar 5.1. Diagram blok rangkaian logika kombinasi

Pada gambar diatas diperlihatkan output rangkaian logika kombinasi merupakan fungsi langsung dari input-inputnya. Output  $f_0$  merupakan fungsi dari input  $i_0$  dan  $i_1$ , dalam hal ini  $f_0$  hanya dipengaruhi oleh kombinasi dari  $i_0$  dan  $i_1$  saja. Demikian pula dengan output-output yang lain.

Begitu pula halnya manusia dalam melakukan berbagai aktifitasnya, tentunya dalam bertindak lebih menekankan kepada logikanya, sehingga akan menghasilkan output berupa hasil pekerjaannya atau hasil aktivitasnya apakah memberi manfaat atau tidak. Sebagaimana dijelaskan dalam QS.Al-Baqarah/2:32.

Terjemahnya: Mereka menjawab: "Maha suci Engkau, tidak ada yang Kami ketahui selain dari apa yang telah Engkau ajarkan kepada kami; Sesungguhnya Engkaulah yang Maha mengetahui lagi Maha Bijaksana." (Departemen Agama, 2005)

# 5.2. Bentuk-bentuk Persamaan Logika